Answer:

7

Step-by-step explanation:

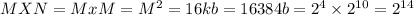

The structure of memory chip is given by multiplying the number of rows and column ie M X N

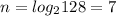

he number of address line required for row decoder is n where M =

or expressed in logarithmic form we have

or expressed in logarithmic form we have

In this case M=N since number of rows is equal to the number of columns

Therefore,

Therefore,

M=128

Since

Therefore, address lines should be at least 7