Answer:

a) First, we need to determine the pipeline stage amounting to the maximum time. In the given case, the maximum time required is 2ns for MEM. In addition, the pipeline register delay=0.1 ns.

Clock cycled time of the pipelined machine= max time+delay

=2ns+0.1 ns

=2.1 ns

b) For any processor, ideal CPI=1. However, since there is a stall after every four instructions, the effective CPI of the new machine is specified by:

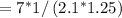

c) The speedup of pipelined machine over the single-cycle machine=avg time per instruction of single cycle/avg time per instruction of pipelined.

Single cycle processor:

CPI=1

Clock period=7 ns

Pipelined processor:

Clock period=2.1 ns

CPI=1.25

Therefore, speedup=

=7/2.625

= 2.67

d) As the number of stages approach infinity, the speedup=k where k is the number of stages in the machine.