Answer:

Following are the solution to the given points:

Step-by-step explanation:

The Memory address value = 64 bit

The Size of the word

In point a:

The offset size

( in 1-word block size)

( in 1-word block size)

The Index size

(as block number =512)

(as block number =512)

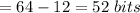

Tag size

In point b:

The offset size

The Index size

Tag size

In point c:

The Ratio at point a

The Ratio at point b