Answer:

Following are the solution to the given question:

Step-by-step explanation:

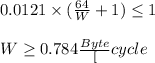

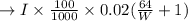

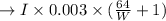

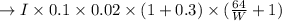

In point 1:

I = number of program code completed.

In such a block of the system memory, the number of iterations to read would be 64/W, while W is the length of its band.

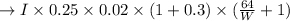

Miss penalty (cycling):

Miss penalty is written for the data cache:

Miss penalty for the cache instruction:

The

, Hit time + miss penalty Hit time:

, Hit time + miss penalty Hit time:

![= I + I * [0.25 * 0.02 + 0.1 * 0.02 + 0.003] * ((64)/(W) + 1) \leq I * 2.](https://img.qammunity.org/2021/formulas/computers-and-technology/college/hcuedphgofufh2brqlmzizqkferlmfcutp.png)

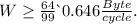

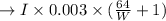

In point 2:

Miss penalty read data cache:

Miss penalty for the data cache:

Read the penalty for miss:

Total runtime = time hit + penalty mismatch

![= I + I * [0.25 * 0.02 * 1.3 + 0.1 * 0.02* 1.3 + 0.003]* ((64)/(W) + 1) \leq 2I](https://img.qammunity.org/2021/formulas/computers-and-technology/college/b53en5jp2pwl5l5j4g28665o3bhsbhaqhv.png)